# **SPICE Model of Memristive Devices with Threshold**

Yuriy V. PERSHIN<sup>1</sup>, Massimiliano DI VENTRA<sup>2</sup>

<sup>1</sup>Department of Physics and Astronomy and USC Nanocenter, University of South Carolina, Columbia, SC 29208, USA <sup>2</sup>Department of Physics, University of California, San Diego, La Jolla, CA 92093-0319, USA

pershin@physics.sc.edu, diventra@physics.ucsd.edu

**Abstract.** Although memristive devices with threshold voltages are the norm rather than the exception in experimentally realizable systems, their SPICE programming is not yet common. Here, we show how to implement such systems in the SPICE environment. Specifically, we present SPICE models of a popular voltage-controlled memristive system specified by five different parameters for PSPICE and NGSPICE circuit simulators. We expect this implementation to find widespread use in circuits design and testing.

### **Keywords**

Memristive devices, memristor, memristor model, threshold dynamics

### 1. Introduction

In the last few years, circuit elements with memory, namely, memristive [1], memcapacitive and meminductive [2] systems have attracted considerable attention from different disciplines due to their capability of non-volatile lowpower information storage, potential applications in analog and digital circuits, and their ability to store and manipulate information on the same physical platform [3]. However, when combined into complex circuits, progress in this field significantly relies on the available tools at our disposal. One such tool is the SPICE simulation environment, commonly used in circuit simulations and testing. While several SPICE models of memristive [4, 5, 6, 7, 8, 9, 10], memcapacitive [6, 11] and meminductive [6, 12] elements are already available, they typically [4, 5, 6, 7, 8] rely on physical models without a threshold (see, e.g., [13, 14]).

Threshold-type switching is instead an extremely important common feature of memristive devices (for examples, see [3]) and, due to physical constraints, likely to be common in memcapacitive and meminductive elements as well [15]. Indeed, it is the threshold-type switching which is responsible for non-volatile information storage, serves as a basis for logic operations [16, 17], etc., and therefore, it can not be neglected. For instance, experimentally demonstrated memristive logic circuits [16] and emerging memory architectures [18] support fixed-threshold modeling [19] of memristive devices. Moreover, the atomic migration responsible for resistance switching in many important experimental systems is induced by the applied field and not by the electric current flow. Therefore, models with voltage threshold [19, 9] are physically better justified than those with the current one [10].

In the present paper we introduce a SPICE model for a memristive device with threshold voltage that has been proposed by the present authors [19]. Using this type of memristive devices, we have already demonstrated and analyzed several electronic circuits including a learning circuit [19], memristive neural networks [20], logic circuits [17], analog circuits [21] and circuits transforming memristive response into memcapacitive and meminductive ones [22]. These previous results thus demonstrate the range of applicability of the selected physical model. As a consequence, we expect its SPICE implementation to find numerous applications as well.

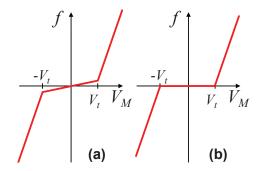

**Fig. 1.** Sketch of the function  $f(V_M)$  for (a)  $\alpha > 0$  and  $\beta > 0$ and (b)  $\alpha = 0$  and  $\beta > 0$ .

### SPICE Model

The equations describing memristive systems can be formulated in the voltage- or current-controlled form [1]. In some cases, a voltage-controlled memristive system can be easily re-formulated as a current-controlled one and vice versa [3]. Let us then focus on voltage-controlled memristive systems whose general definition (for an  $n^{th}$ -order voltagecontrolled memristive system) is given by the following relations

$$I(t) = R_M^{-1}(X, V_M, t) V_M(t),$$

$$\dot{X} = f(X, V_M, t)$$

(2)

$$\dot{X} = f(X, V_M, t) \tag{2}$$

where X is the vector representing n internal state variables,  $V_M(t)$  and I(t) denote the voltage and current across the device, and  $R_M$  is a scalar, called the *memristance* (for memory resistance).

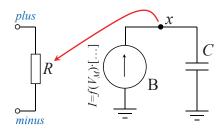

**Fig. 2.** Schematic of the SPICE model. The memristive device functionality is organized as a subcircuit consisting of a behavioral resistor *R*, current source B and capacitor *C*. The voltage across the capacitor (at the node *x*) defines the resistance of *R*.

A specific realization of a voltage-controlled memristive system *with threshold* has been suggested by the present authors in [19]. Such a memristive system is described by

$$I = X^{-1}V_{M},$$

$$\frac{dX}{dt} = f(V_{M}) \left[ \theta(V_{M}) \theta(R_{off} - X) + \theta(-V_{M}) \theta(X - R_{on}) \right],$$

(4)

with

$$f(V_M) = \beta V_M + 0.5 (\alpha - \beta) [|V_M + V_t| - |V_M - V_t|]$$

(5)

where  $V_t$  is the threshold voltage,  $R_{on}$  and  $R_{off}$  are limiting values of the memristance  $R_M \equiv X$ , and the  $\theta$ -functions (step functions) are used to limit the memristance to the region between  $R_{on}$  and  $R_{off}$ . The important model parameters are the coefficients  $\alpha$  and  $\beta$  that characterize the rate of memristance change at  $|V_M| < V_t$  and  $|V_M| > V_t$ , respectively. These two coefficients define the slopes of the  $f(V_M)$  curve below and above the threshold (see Fig. 1). When  $\alpha = 0$  (Fig. 1(b)), the device state changes only if  $|V_M| > V_t$ . Note that Eqs. (3)-(5) are written in such a way that a positive/negative voltage applied to the top terminal with respect to the bottom terminal denoted by the black thick line always tends to increase/decrease the memristance  $R_M$  (the opposite convention has been used in [19]).

Fig. 3. Memristive device directly connected to a voltage source V(t).

The SPICE model for these devices is formulated following the general idea of Ref. [4]. For NGSPICE circuit simulator, the memristive system is realized as a sub-circuit

combining a behavioral resistor R (a resistor whose resistance can be specified by an expression), a current source  $\uparrow$ , and a capacitor C. Table 1 presents the code of the subcircuit. Its second line (Bx...) defines the current source with the current specified through ternary functions. (A ternary function is defined in the code as a ? b : c, which means "IF a, THEN b, ELSE c" [23].) The purpose of these functions is to limit  $R_M$  between  $R_{on}$  and  $R_{off}$ . The third line of the code in Tab. 1 specifies the capacitor C(Cx...) with an initial condition. The fourth line (Rmem ...) defines the behavioral resistor whose resistance takes the same numerical value as the voltage across the capacitor. The next line (.func ...) provides the function f according to (5). We have not experienced any convergence problems using Tab. 1 model with NGSPICE simulator that potentially could result from "IF-THEN" statements. Clearly, (3)-(5) could be programmed differently, employing smoothing functions (e.g., arctan(), sigmoid or similar function) as we do below in the case of PSPICE simulator model. Moreover, instead of "IF...THEN" statement in Tab. 1, one can use a step function based expression. In this case, the "Bx ..." line of the code should be replaced with "Bx 0 x  $I=\{f1(V(pl,mn))*(u(V(pl,mn))*u(Roff-$ V(x)+u(V(mn,pl))\*u(V(x)-Ron))".

For PSPICE circuit simulator, the SPICE model of memristive device with threshold is formulated slightly differently without the use of behavioral resistor. Instead, we employ an additional current source playing the role of behavioral resistor [24]. In addition, in order to avoid convergence problems, the function f in (5) should be smoothed. In the most important case of  $\alpha = 0$ , the smoothing of f is straightforward. Tab. 2 presents the code for PSPICE circuit simulator for this case. In Tab. 2, nu1 and nu2 are smoothing parameters used in smoothed step functions f2 and f3 (although we prefer to use different smoothing parameters for functions of voltages and resistances, a common smoothing function could also be used). We have verified that simulation results are identical in both versions of SPICE and that PSPICE code is also compatible with LTspice circuit simulator. In addition, we note that the value of beta in Tab. 2 was selected to match switching times of real memristive devices that are in nanoseconds range. We suggest to select the maximum allowable time step not exceeding 0.01ns when using this value of beta.

### 3. Example

Let us consider a memristive device with threshold directly connected to a sinusoidal voltage source  $V(t) = V_0 \sin(2\pi vt)$  as presented in Fig. 3. The circuit simulations are performed as a transient analysis of the circuit taking into account initial conditions (the *uic* option of *.tran*) within the NGSPICE circuit simulator. In our simulations, we consider two different types of memristive devices with threshold corresponding to two cases of functions  $f(V_M)$  as presented in Fig. 1. In the first case (that can be dubbed as a memristive device with a *soft threshold*) the coefficients  $\alpha, \beta > 0$

```

.subckt memristor pl mn PARAMS: Ron=1K Roff=10K Rinit=5K alpha=0 beta=1E13 Vt=4.6

Bx 0 x I='(f1(V(pl,mn))>0)_&&_(V(x)<Roff)_?_{f1}(V(pl,mn))}:_(f1(V(pl,mn))<0)_&&_(V(x)>Ron)_?_{f1}(V(pl,mn))}:_(0)'

Cx x 0 1 IC={Rinit}

R0 pl mn 1E12

Rmem pl mn r={V(x)}

.func f1(y)={beta*y+0.5*(alpha-beta)*(abs(y+Vt)-abs(y-Vt))}

.ends

```

**Tab. 1.** NGSPICE implementation of Eqs. (3)-(5).

```

.subckt memristor pl mn PARAMS: Ron=1K Roff=10K Rinit=5K beta=1E13 Vtp=4.6 Vtm=4.6 nu1=0.0001 nu2=0.1

Gx 0 x value={f1(V(pl)-V(mn))*(f2(f1(V(pl)-V(mn)))*f3(Roff-V(x))+f2(-f1(V(pl)-V(mn)))*f3(V(x)-Ron))}

Raux x 0 1E12

Cx x 0 1 IC={Rinit}

Gpm pl mn value={(V(pl)-V(mn))/V(x)}

.func f1(y)={beta*(y-Vtp)/(exp(-(y-Vtp)/nu1)+1)+beta*(y+Vtm)/(exp(-(-y-Vtm)/nu1)+1)}

.func f2(y1)={1/(exp(-y1/nu1)+1)}

.func f3(y)={1/(exp(-y/nu2)+1)}

.ends

```

**Tab. 2.** PSPICE implementation of (3)-(5) for  $\alpha = 0$ . For the sake of versatility, Vtp and Vtm are introduced to define voltage thresholds separately for opposite polarities.

and  $\alpha < \beta$ . In this case, the memristance changes at any  $V \neq 0$ . However, the change is faster when the applied voltage magnitude is above the threshold voltage ( $|V| > V_t$ ). In the second case (Fig. 1(b)),  $\alpha = 0$ . Consequently, the memristance changes only when the applied voltage exceeds the threshold voltage ( $|V| > V_t$ ). This second case is closer to the actual behavior of many experimentally realizable memristive systems [3]. We call this type of systems as memristive devices with *hard threshold*.

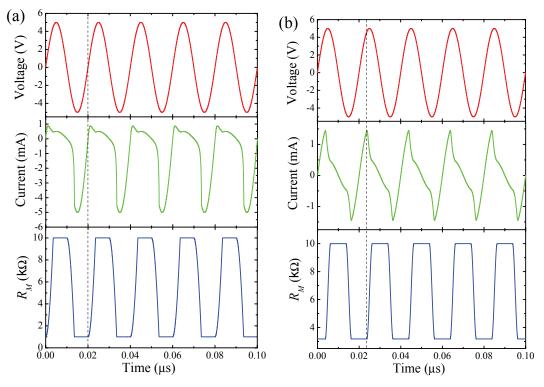

Fig. 4 presents selected results of our simulations showing the circuit dynamics at long times (the initial transient interval is omitted). We consider two types of memristive devices - one with a soft and another with hard thresholds ( $\alpha = 0.1\beta$  and  $\alpha = 0$ , respectively) – and plot the applied voltage, current and memristance as functions of time for these two cases at a frequency v = 0.05 GHz. Clearly, in both cases, the current through the device is not of the simple sine form. The plot of memristance as a function of time demonstrates that the range of memristance change in (a) is larger than in (b) (actually, in (a),  $R_M$  switches between  $R_{on}$ and  $R_{off}$ ). The vertical dashed line in Fig. 4(a) helps noticing that in Fig. 4(a) the memristance starts changing as soon as the sign of applied voltage changes. In Fig. 4(b), instead, the change of  $R_M$  occurs solely when  $|V| > V_t$ . As a consequence, the shapes of  $R_M(t)$  in Fig. 4(a) and (b) are slightly different, and the steps in  $R_M(t)$  in Fig. 4(b) are shifted along the horizontal axis compared to those in Fig. 4(a).

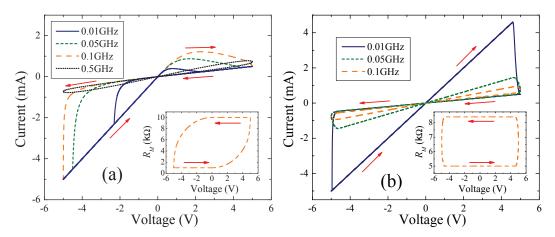

The current as a function of voltage at several selected values of  $\nu$  is plotted in Fig. 5. Clearly, these curves are typical frequency-dependent pinched hysteresis loops [1, 2]. The character of the loops for memristive systems with hard and soft thresholds is slightly different. While for memristive systems with soft threshold the curve for the lowest frequency has the smallest loop span, the situation for the memristive system with hard threshold is opposite: the largest loop span occurs at the lowest frequency. This result, how-

ever, is not surprising if we take into account the fact that in the memristive system with soft threshold the change of  $R_M$  occurs at lower voltages. Moreover, the insets of Fig. 5 demonstrate the memristance  $R_M(t)$  as a function of V(t) at a particular frequency. It is not difficult to notice that in the case of the memristive system with hard threshold (shown in the inset of Fig. 5(b)),  $R_M$  changes only when |V| exceeds  $V_t = 4.6 \text{ V}$ .

### 4. Conclusions

We have developed and tested a SPICE model of memristive devices with threshold voltage. In this model, the limiting conditions for the memristance are realized using ternary functions which adhere more closely to the actual physical situation, compared with the window functions approach previously suggested [14]. The memristive device is realized as a sub-circuit consisting of several elements. While the present model is based on a single internal state variable, X, it can be easily generalized to more complex physical models involving several internal state variables. We would like to note that the NGSPICE model presented in Table 1 was included into the last distribution of NGSPICE [23]. Moreover, different convergence and simulation issues of memelements in SPICE will be considered in our future publication. Finally, we note that threshold models of memcapacitive and meminductive systems can be implemented in the SPICE environment in a similar way.

## Acknowledgements

This work has been partially supported by NSF grants No. DMR-0802830 and ECCS-1202383, and the Center for Magnetic Recording Research at UCSD.

Fig. 4. Time evolution of the applied voltage V(t), current I(t) and memristance  $R_M(t)$  for memristive devices with (a) soft (α = 0.1β), and (b) hard (α = 0) thresholds. The vertical dashed lines - corresponding to the onset of switching - serve as guide to the eye. The simulations parameters are as follows: the applied voltage amplitude  $V_0 = 5$  V, v = 0.05 GHz,  $R_{on} = 1$  kΩ,  $R_{off} = 10$  kΩ,  $R_M(t = 0) = 5$  kΩ,  $R_{off} = 10^{10}$  kΩ/(V s),  $R_{off} = 10^{10}$  kΩ/(P s)

Fig. 5. Frequency-dependent hysteresis loops for memristive devices with soft (a) and hard (b) thresholds. The simulations parameters are as in Fig. 4 except of  $\nu$ . The applied voltage frequencies  $\nu$  are indicated on the plots. The insets (calculated at 0.1 GHz sine voltage frequency) show the memristance as a function of applied voltage. The inset in (b) demonstrates that in the case of the hard threshold the memristance changes only when the absolute value of the applied voltage exceeds the threshold voltage  $V_t$ .

### References

- [1] CHUA, L. O., KANG, S. M. Memristive devices and systems. *Proceedings of the IEEE*, 1976, vol. 64, no. 2, p. 209 223.

- [2] DI VENTRA, M., PERSHIN, Y. V., CHUA, L. O. Circuit elements with memory: Memristors, memcapacitors, and meminductors. *Pro*ceedings of the IEEE, 2009, vol. 97, no. 10, p. 1717 - 1724.

- [3] PERSHIN, Y. V., DI VENTRA, M. Memory effects in complex materials and nanoscale systems. *Advances in Physics*, 2011, vol. 60, p. 145 227.

- [4] BIOLEK, Z., BIOLEK, D., BIOLKOVA, V. SPICE model of memristor with nonlinear dopant drift. *Radioengineering*, 2009, vol. 18, no. 2, p. 210 214.

- [5] BENDERLI, S., WEY, T. A. On SPICE macromodelling of TiO2 memristors. *Electronics Letters*, 2009, vol. 45, no. 7, p. 377 - 378.

- [6] BIOLEK, Z., BIOLEK, D., BIOLKOVA, V. SPICE modeling of memristive, memcapacitative and meminductive systems. In *Proceedings of European Conference on Circuit Theory and Design* (ECCTD). Antalya (Turkey), 2009, p. 249 - 252.

- [7] SHIN, S., KIM, K., KANG, S.-M. Compact models for memristors based on charge-flux constitutive relationships. *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, 2010, vol. 29, p. 590.

- [8] RAK, A., CSEREY, G. Macromodeling of the memristor in SPICE. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2010, vol. 29, no. 4, p. 632 - 636.

- [9] YAKOPCIC, C., TAHA, T. M., SUBRAMANYAM, G., PINO, R. E., ROGERS, S. A memristor device model. *IEEE Electron Device Letters*, 2011, vol. 32, no. 10, p. 1436 - 1438.

- [10] KVATINSKY, S., FRIEDMAN, E. G., KOLODNY, A., WEISER, U. C. TEAM: Threshold adaptive memristor model. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2013, vol. 60, no. 1, p. 211 - 221.

- [11] BIOLEK, D., BIOLEK, Z., BIOLKOVA, V. SPICE modelling of memcapacitor. *Electronics Letters*, 2010, vol. 46, no. 7, p. 520 - 522.

- [12] BIOLEK, D., BIOLEK, Z., BIOLKOVA, V. PSPICE modeling of meminductor. *Analog Integrated Circuits and Signal Processing*, 2011, vol. 66, no. 1, p. 129 - 137.

- [13] STRUKOV, D. B., SNIDER, G. S., STEWART, D. R., WILLIAMS, R. S. The missing memristor found. *Nature*, 2008, vol. 453, p. 80 -83.

- [14] JOGLEKAR, Y. N., WOLF, S. J. The elusive memristor: properties of basic electrical circuits. *European Journal of Physics*, 2009, vol. 30, p. 661.

- [15] DI VENTRA, M., PERSHIN, Y. V. On the physical properties of memristive, memcapacitive, and meminductive systems. *Nanotechnology (in press)*, 2013; arXiv:1302.7063.

- [16] BORGHETTI, J., SNIDER, G. S., KUEKES, P. J., YANG, J. J., STEWART, D. R., WILLIAMS, R. S. 'Memristive' switches enable 'stateful' logic operations via material implication. *Nature*, 2010, vol. 464, p. 873 - 876.

- [17] PERSHIN, Y. V., DI VENTRA, M. Neuromorphic, digital and quantum computation with memory circuit elements. *Proceedings of the IEEE*, 2012, vol. 100, no. 6, p. 2071 2080.

- [18] LINN, E., ROSEZIN, R., WASER, R. Complementary resistive switches for passive nanocrossbar memories. *Nature Materials*, 2010, vol. 9, p. 403 - 406.

- [19] PERSHIN, Y. V., LA FONTAINE, S., DI VENTRA, M. Memristive model of amoeba learning. *Physical Review E*, 2009, vol. 80, no. 2, p. 021926.

- [20] PERSHIN, Y. V., DI VENTRA, M. Experimental demonstration of associative memory with memristive neural networks. *Neural Net*works, 2010, vol. 23, no. 7, p. 881 - 886.

- [21] PERSHIN, Y. V., DI VENTRA, M. Practical approach to programmable analog circuits with memristors. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 2010, vol. 57, no. 8, p. 1857 1864.

- [22] PERSHIN, Y. V., DI VENTRA, M. Memristive circuits simulate memcapacitors and meminductors. *Electronics Letters*, 2010, vol. 46, no. 7, p. 517 518.

- [23] NENZI, P., VOGT, H. Ngspice Users Manual, version 25plus. 2013. [Online] Available at: http://ngspice.sourceforge.net/docs/ngspice-manual.pdf

- [24] BASSO, C. SPICE analog behavioral modeling of variable passives. *Power Electronics Technology*, 2005, vol. 31, no. 3, p. 57 59.

#### About Authors...

**Yuriy V. PERSHIN** was born in Russia. He received his Ph.D. degree in theoretical physics from the University of Konstanz, Konstanz, Germany, in 2002. His research interests span broad areas of nanotechnology, including physics of semiconductor nanodevices, spintronics, and biophysics.

Massimiliano DI VENTRA was born in Italy. He received his Ph.D. degree in theoretical physics from the Ecole Polytechnique Federale de Lausanne, Switzerland, in 1997. His research interests are in the theory of electronic and transport properties of nanoscale systems, non-equilibrium statistical mechanics, DNA sequencing/polymer dynamics in nanopores, and memory effects in nanostructures for applications in unconventional computing and biophysics.