### **Analysis of Residue Probability Density Function and Comparator Offset Error in Pipelined ADCs**

Esmaeil FATEMI-BEHBAHANI, Ebrahim FARSHIDI, Karim ANSARI-ASL

Dept. of Electrical Engineering, Faculty of Engineering, Shahid Chamran University of Ahvaz, Ahvaz, Iran

e-fatemi@phdstu.scu.ac.ir, {farshidi, karim.ansari}@scu.ac.ir

Manuscript received June 26, 2015

Abstract. This paper presents a new approach to analyze the convergence of residue probability density function (pdf) in pipelined ADCs. Compared to the previous approaches, in the proposed approach, in addition to the analysis of residue pdfs for different input densities, the analysis of the sub-ADC comparator offsets impact on output pdf is possible. Using Fourier analysis, it will be shown that the residue density converges to uniformity. In the half-bit redundant structure, residue pdf concentrates in the center half of the stage full-scale range and 6 dB of extra resolution can be gained. Also, the share of each stage in this resolution improvement is investigated. Examining the sub-ADC threshold offsets impact on residue pdfs, it is observed that with respect to the impact on converter additional resolution, the final stages offset errors are more significant than the first stages offsets.

### Keywords

Comparator offset error, half-bit redundancy, pipelined ADC, power spectral density (PSD), probability density function (pdf), quantization noise

#### 1. Introduction

Multistage analog to digital converters (ADCs) such as pipelined, algorithmic (cyclic), and successive approximation register (SAR), are widely used in medium to high resolution and bandwidth applications. In these architectures, the analog to digital conversion is performed by using one or several successive simple stages in a way that makes it possible to compromise between speed, power consumption, resolution, and circuit area [1–5].

One of very important issues in analog to digital converters is the quantization noise theory, in which the required and sufficient conditions of the uniformity of the noise distribution have been described using quantizing theorems. Quantizing theorems, similar to the sampling theorem but based on the sampling of the probability density function (pdf), clarify the required conditions of signal characteristic function in details [6], [7]. Based on this theory, the output quantization noise of a uniform quantizer is almost white with uniform distribution [6], [7]. In [8], the required and sufficient conditions for having uniform and white output quantization noise are expressed.

Redundant pipelined ADC is a non uniform quantizer. Few studies have been carried out on the analysis of quantization noise specified for this converter. In [9], it has been shown that with the passage of signal from different stages in full-bit and half-bit redundant pipelined converter, the residue density converges to uniformity. In a full-bit pipelined structure it also has been shown that the residue joint probability density function at different times converges to uniformity. This indicates that residue signals become asymptotically independent in full-bit pipelined ADC. Though that study has been presented for any input signal pdf, it cannot be extended to the nonideal stages [9].

In [10] assuming an input with uniform density and analysis of stages residue pdfs, it has been shown that due to the residue density being centered in the middle half of the last stage full-scale range, one bit of extra resolution in a half-bit redundant structure can be achieved. An analysis of sub-ADC offset errors has also been performed and the tolerant threshold region in order to obtain the maximum extra resolution has been presented. This is the advantage of this method but its drawback is considering uniform input pdf, a condition that is not always guaranteed in realities; thus, its results are dependent on such condition.

In this paper, a new approach to analysis of the residue signal pdf in different stages of full-bit and half-bit redundant pipelined ADCs is proposed. In this approach, in addition to the analysis of the residual densities for each input with an arbitrary pdf, it is possible to extract the statistical properties of the quantization noise such as uniformity and independence from the input and each other, at different times. It also makes it possible to examine the impact of sub-ADC offset errors on the residual densities. This has been performed by analyzing the residue signal pdf and mapping input to output pdf stage by stage. To this end, the fundamental theorem for function of a random variable [11] was exploited and the propagation of the residual pdf in successive stages with full-bit and half-bit redundant architectures is shown. By extending the output pdf into a periodic signal and using Fourier domain analysis, it will be shown than residue pdf converges to a uniform distribution. It will be illustrated that in pipelined ADC with half-bit redundant structure, 6 dB extra resolution can be achieved that the share of each stage in such re-

DOI: 10.13164/re.2016.0208 SYSTEMS

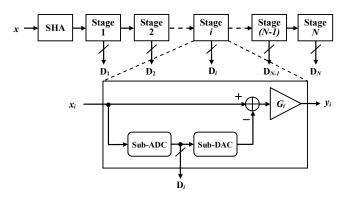

Fig. 1. Pipelined ADC architecture.

solution improvement will be shown. It is also observed that the offset of sub-ADC threshold voltage may cause quantization leakage in the converter stage, where if it is not compensated, the converter resolution improvement will be less than 6 dB. Therefore, an allowable offset range of sub-ADC comparator in various stages is determined in a way that no leakage is formed in converter resolution.

This paper is organized as follows. In Sec. 2, the fundamental theorem for function of a random variable is introduced. Section 3 investigates the residue densities convergence in the full-bit pipelined ADC. Section 4 describes the residue pdf propagation in the half-bit redundant structure and the share of each stage in ADC resolution improvement. In Sec. 5, the comparator offset impact on residue pdf in the half-bit redundant stages and in Sec. 6, a comparison of the proposed approach with previous studies is presented. A brief conclusion is drawn in Sec. 7.

### 2. Function of a Random Variable

The architecture of a pipelined converter is shown in Fig. 1. This ADC consists of an input sample-and-hold amplifier (SHA) and a number N of pipelined stages. All signals are normalized to  $V_{ref}$  so the ADC dynamic range is [-1, 1]. In the ith stage, the flash sub-ADC generates an  $M_i$ -level digital estimation  $D_i$  of the stage input  $x_i$  by comparing it to  $(M_i$ -1) threshold levels. Using a sub-DAC, this digital word is then converted to an analog signal and is subtracted from the stage input  $x_i$ . This difference is amplified with an interstage gain  $G_i$  to produce a residue signal  $y_i$  which is used as the input  $x_{i+1}$  of the next stage.

One important property of the pipelined ADC is converting analog to digital by the aid of a series successive simple stages. This property makes it possible to analyze quantization noise of the converter stage by stage. Since successive stages are similar, analyzing and extracting the converter residue characteristics are easier than those of other ADC types. This is done by mapping each stage input pdf to its output pdf and using this feature for easier analysis of the noise distribution convergence to the uniform distribution.

Similarly, one of the important issues in probability, random variables and stochastic processes, is finding the distribution of a function of a random variable. This can be performed by using the fundamental theorem for function of a random variable. Assuming that x is a random variable with the probability density function  $f_x(x)$ , if this random variable is passed through a system with characteristic y = g(x), the output pdf can be obtained by [11]:

$$f_{y}(y) = \sum_{i} \frac{f_{x}(x_{i})}{|g'(x_{i})|}$$

(1)

where  $x_i$  (i = 1,2,...) are real roots of y = g(x) for any y.

# 3. Residue pdf Propagation in Ideal Nonredundant Stages

The input-output characteristic of each stage in ideal 1-bit/stage pipelined ADC stage is

$$x_{i+1} = y_i = \begin{cases} 2(x_i + 1/2) & -1 < x_i < 0 \\ 2(x_i - 1/2) & 0 < x_i < 1. \end{cases}$$

(2)

Using (1) for the input pdf  $f_x(x)$ , the pipeline Nth stage output pdf is obtained as follows [12]:

$$f_{y_N}(y) = \begin{cases} \frac{1}{M} \sum_{m=0}^{M-1} f_x \left( \frac{y - (2m + 1 - M)}{M} \right) & -1 < y < 1 \\ 0 & \text{otherwise} \end{cases}$$

where  $M=2^N$ . It can be observed that firstly, input pdf is stretched by M and then output pdf is obtained by averaging M copies of this stretched density function.

Since  $f_x(x)$  and  $f_{yN}(y)$  are nonzero only over [-1, +1], they can be extended into periodic signals  $f_x(x)$  and  $f_{yN}(y)$  with period 2 and Fourier series coefficients  $a_k$  and  $b_k$  respectively. The Fourier series representation of these periodic signals can be written as

$$\widetilde{f}_x(x) = \sum_{k = -\infty}^{+\infty} a_k e^{j\pi kx} \Leftrightarrow a_k = \frac{1}{2} \int_{-1}^{+1} f_x(x) e^{-j\pi kx} dx \tag{4}$$

and

$$\widetilde{f}_{y_N}(y) = \sum_{k = -\infty}^{+\infty} b_k e^{j\pi ky} \iff b_k = \frac{1}{2} \int_{-1}^{+1} f_{y_N}(y) e^{-j\pi ky} dy.$$

(5)

By substituting (3) in (5),  $b_k$  can be calculated as

$$b_{k} = \frac{1}{2M} \int_{-1}^{+1} \sum_{m=0}^{M-1} f_{x} \left( \frac{y - (2m+1-M)}{M} \right) e^{-j\pi ky} dy$$

$$= \frac{1}{2} \sum_{m=0}^{M-1} \left( \int_{1-\frac{2m}{M}}^{1-\frac{2m}{M}} f_{x}(x) e^{-j\pi Mkx} dx \right) e^{-j\pi k(2m+1-M)} . \tag{6}$$

As regards  $\exp(-j\pi k(2m + 1 - M)) = (-1)^k$

$$b_k = \frac{(-1)^k}{2} \sum_{m=0}^{M-1} \int_{1-\frac{2(m+1)}{M}}^{1-\frac{2m}{M}} f_x(x) e^{-j\pi Mkx} dx$$

$$= \frac{(-1)^k}{2} \int_{-1}^{+1} f_x(x) e^{-j\pi Mkx} dx . \tag{7}$$

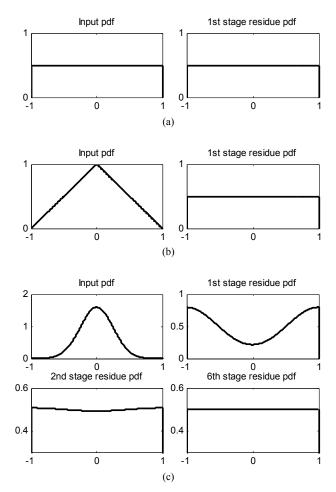

**Fig. 2.** The stages residue pdfs of a 1-bit/stage pipelined converter: (a) the uniform input pdf, (b) the triangular input pdf, (c) the truncated Gaussian input pdf with  $\mu = 0$  and  $\sigma = 0.25$ .

Comparing (4) and (7) reveals that

$$b_k = (-1)^k a_{Mk}. (8)$$

It can be observed that kth Fourier coefficient of  $f_{yN}(y)$  is equal to (Mk)th harmonic of  $f_x(x)$ . Hence, the last stage residue pdf retains only the Fourier series coefficients which are integer multiples of M. So, after propagating through a sufficient number of stages, only the DC component

$$b_0 = a_0 = \frac{1}{2} \int_{-1}^{+1} f_x(x) dx = \frac{1}{2}$$

(9)

is preserved and subsequent harmonics are weeded out. It is clear that with increasing the total number of bits of the ADC (*N*), the last stage residue pdf converges to the uniform distribution:

$$f_{y_N}(y) = \begin{cases} 1/2 & -1 < y < 1 \\ 0 & \text{otherwise.} \end{cases}$$

(10)

The stages residue pdfs of a 1-bit/stage pipelined ADC for different input densities are shown in Fig. 2. It can be seen that for the uniform and triangular input pdfs, the residue pdfs of the all subsequent stages are uniform. For the truncated Gaussian input, passing the signal through

Fig. 3. The stages residue pdfs of an 11-bits pipelined converter for a truncated zero mean Gaussian input with  $\sigma = 0.01$ .

through each stage, the standard deviation of its elements will be increased as shown in Fig. 2(c), where the residue pdf converges to a uniform distribution.

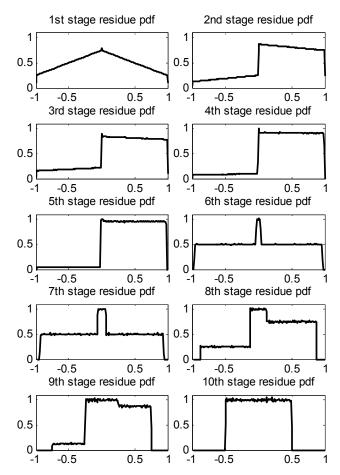

To illustrate the results, an 11-bits ideal pipelined converter including  $10\times1$ -bit/stage with 1-bit backend flash was simulated. The residual pdfs of the different stages for a truncated zero mean Gaussian input with  $\sigma=0.01$  are shown in Fig. 3. As it is expected, after many stages, residue probability density function converges to the uniform distribution over [-1, +1].

# 4. Residue pdf Propagation in Ideal Half-bit Redundant Stages

For an ideal 1.5-bit/stage pipelined ADC, the stage input-output characteristic is as following expression:

$$x_{i+1} = y_i = \begin{cases} 2(x_i + 1/2) & -1 < x_i < -1/4 \\ 2x_i & -1/4 < x_i < 1/4 \\ 2(x_i - 1/2) & 1/4 < x_i < 1. \end{cases}$$

(11)

Using (1) for the input pdf  $f_x(x)$ , the pipeline Nth stage output pdf is obtained as follows [12]:

$$f_{y_N}(y) = \begin{cases} \frac{1}{2^N} f_x \left( \frac{y - (2^N - 1)}{2^N} \right) & -1 < y < -\frac{1}{2} \\ \frac{1}{2^N} \sum_{m = -(2^N - 1)}^{(2^N - 1)} f_x \left( \frac{y - m}{2^N} \right) & -\frac{1}{2} < y < \frac{1}{2} \\ \frac{1}{2^N} f_x \left( \frac{y + (2^N - 1)}{2^N} \right) & \frac{1}{2} < y < 1. \end{cases}$$

(12)

It can be observed that by increasing N, the output pdf concentration in center half of the stage full-scale range is

increased and out of this range exponentially converges to zero. Since after a sufficient number of stages,  $f_{yN}(y)$  is fully concentrated over [-1/2, 1/2], by repeating the middle half of the last stage full-scale range it can be extended into a periodic signal  $f_{yN}(y)$  with period 1 and Fourier series coefficients  $c_k$

$$\hat{f}_{y_{N}}(y) = \sum_{k=-\infty}^{+\infty} c_{k} e^{j2\pi ky} \iff c_{k} = \int_{-\frac{N}{2}}^{+\frac{N}{2}} f_{y_{N}}(y) e^{-j2\pi ky} dy . (13)$$

By substituting (12) in (13),  $c_k$  can be calculated as

$$c_{k} = \frac{1}{M} \int_{-\frac{1}{2}}^{-\frac{1}{2}} \sum_{m=-(M-1)}^{M-1} f_{x} \left( \frac{y-m}{M} \right) e^{-j2\pi ky} dy$$

$$= \sum_{m=-(M-1)}^{M-1} \left( \int_{-\frac{m}{M} - \frac{1}{2M}}^{-\frac{m}{2M}} f_{x}(x) e^{-j2\pi Mkx} dx \right) e^{-j2\pi mk}$$

(14)

where  $M = 2^N$ . As regards  $\exp(-j2\pi mk) = 1$

$$c_k = \int_{-1 + \frac{1}{2M}}^{+1 - \frac{1}{2M}} f_x(x) e^{-j2\pi Mkx} dx . \tag{15}$$

Comparing (4) and (15) reveals that with increasing the total number of bits of the converter (N),  $c_k$  converges to  $2a_{2Mk}$

$$c_k \to 2a_{2Mk}. \tag{16}$$

It means that the last stage residue pdf retains only the Fourier series coefficients which are integer multiples of 2M. So, after propagating through a sufficient number of stages, only the DC component

$$c_0 = 2a_0 = \int_{-1}^{+1} f_x(x) dx = 1$$

(17)

is preserved and subsequent harmonics are weeded out. Therefore, for many stages, final pdf

$$f_{y_N}(y) = \begin{cases} 1 & -1/2 < y < 1/2 \\ 0 & \text{otherwise} \end{cases}$$

(18)

is distributed uniformly over [-1/2, 1/2]. It is clear that by halving the quantization noise amplitude, the power of output noise will be 1/4 of the pipelined ADC with the nonredundant stages. The result indicates that the 1.5-bit/stage pipelined ADC structure makes it possible to achieve 6 dB of extra resolution. Similar results relating to residue pdf analysis of 1.5-bit/stage pipelined ADC are obtained in [9] and [10].

Another noteworthy point is that quantization noise distribution converges to uniformity for any input pdf. This indicates that the converter quantization noise and input signal are independent. On the other hand, in the calibration of pipelined converter by using a pseudo-random sequence, it is assumed that dither and the converter quantization noise are uncorrelated [13–15]. Since the quantization noise pdf, regardless of using or not using of dither, always converges to the uniform pdf, quantization noise and dither are independent of each other and are uncorrelated.

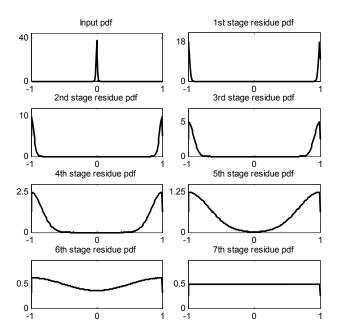

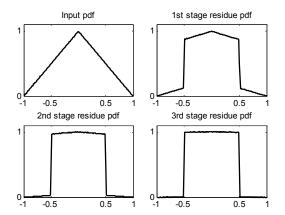

**Fig. 4.** The stages residue pdfs of a 1.5-bit/stage pipelined ADC for: (a) the uniform input pdf (b) the truncated Gaussian input pdf with  $\mu = 0$  and  $\sigma = 1/2$ .

The stages residue pdfs of a 1.5-bit/stage pipelined ADC for different input densities are shown in Fig. 4. It can be seen that residue pdf converges to the uniform distribution over [-1/2, 1/2]. So, an important benefit of half-bit redundant converters is the obtaining 6 dB extra resolution, where the share of each stage in this improvement can be determined by calculating the output quantization noise power.

The output quantization noise power of each stage is

$$P_{\varepsilon} = \int \varepsilon_q^2 f(\varepsilon_q) d\varepsilon_q \tag{19}$$

where  $\varepsilon_q$  and  $f(\varepsilon_q)$  denote the stage output quantization noise and its pdf, respectively. If  $P_{\varepsilon_R}$  and  $P_{\varepsilon}$  denote the output quantization noise power of each stage in half-bit redundant and nonredundant pipelined converters, respectively, the SQNR improvement of the half-bit redundant structure ( $\Delta SONR_R$ ) after each stage, is

$$\Delta SQNR_R = 10 \log_{10} \left( \frac{P_{\varepsilon}}{P_{\varepsilon_R}} \right). \tag{20}$$

For uniform and triangular input pdfs, the *SQNR* improvement of the half-bit redundant structure after passing different stages is shown in Tab. 1.

To illustrate the results, a simulation was performed for an 11-bits ideal pipelined converter including 10×1.5-bit

| Stage | Uniform Input pdf | Triangular Input pdf |

|-------|-------------------|----------------------|

| 1     | 2.04              | 5.06                 |

| 2     | 3.59              | 5.76                 |

| 3     | 4.64              | 5.95                 |

| 4     | 5.27              | 6.00                 |

| 5     | 5.63              | 6.02                 |

| 6     | 5.82              | 6.02                 |

| 7     | 5.92              | 6.02                 |

| 8     | 5.97              | 6.02                 |

| 9     | 6.00              | 6.02                 |

| 10    | 6.01              | 6.02                 |

**Tab. 1.** The SQNR improvement in the 1.5-bit/stage pipelined converter [12].

stages with 1-bit backend flash. The residual distributions of the different stages for a triangular input pdf are shown in Fig. 5. It can be observed that residue pdf converges to the uniform distribution over [-1/2, 1/2]. So, 6 dB resolution improvement is achieved in 1.5-bit/stage structure.

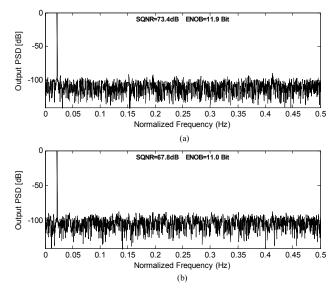

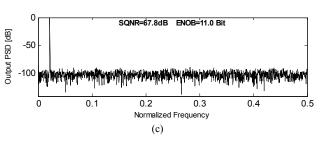

By simulating an ideal 11-bit flash ADC, output power spectral densities (PSDs) of these two converters for a full-scale sinusoidal input are shown in Fig. 6. Comparing their *SQNRs* and *ENOBs* shows that the half-bit redundant pipelined ADC has higher resolution.

# 5. Offset Analysis in Residue pdf Propagation

It would be of interest to extend the proposed analysis to nonideal stages. Taking into account that the main reason of using redundancy in pipelined converters is the nonidealities impact, especially of sub-ADC offset errors [16–18], the offset impact on the residue pdf is studied.

Assuming that the 1.5-bit pipelined ADC stage has an offset of  $\delta$  in +1/4 threshold level, (11) can be written as

$$x_{i+1} = y_i = \begin{cases} 2(x_i + 1/2) & -1 < x_i < -1/4 \\ 2x_i & -1/4 < x_i < 1/4 + \delta \end{cases}$$

(21)

$$2(x_i - 1/2) & 1/4 + \delta < x_i < 1.$$

Using (1), the pipeline first stage output pdf is [12]  $f_{y_i}(y) =$

$$\begin{cases}

\frac{1}{2} f_{x_{i}} \left( \frac{y-1}{2} \right) & -1 < y < -\frac{1}{2} \\

\frac{1}{2} \left( f_{x_{i}} \left( \frac{y-1}{2} \right) + f_{x_{i}} \left( \frac{y}{2} \right) \right) & -\frac{1}{2} < y < -\frac{1}{2} + 2\delta \\

\frac{1}{2} \left( f_{x_{i}} \left( \frac{y-1}{2} \right) + f_{x_{i}} \left( \frac{y}{2} \right) & -\frac{1}{2} + 2\delta < y < \frac{1}{2} \\

+ f_{x_{i}} \left( \frac{y+1}{2} \right) \right) & \frac{1}{2} < y < \frac{1}{2} + 2\delta \\

\frac{1}{2} \left( f_{x_{i}} \left( \frac{y}{2} \right) + f_{x_{i}} \left( \frac{y+1}{2} \right) \right) & \frac{1}{2} < y < \frac{1}{2} + 2\delta < y < 1.

\end{cases} \tag{22}$$

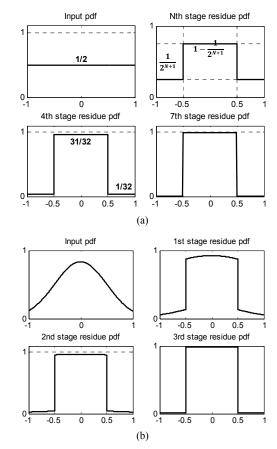

Fig. 5. The stages residue pdfs of an 11-bits ideal pipelined converter including 10×1.5-bit/stage and 1-bit backend for a triangular input pdf.

Fig. 6. Output PSD of: (a) 11-bits pipelined converter including 10×1.5-bit/stage with 1-bit backend flash, (b) 11-bits flash converter.

Comparing (22) and (12), we observe the quantization leakage beyond  $\pm 1/2$  which decreases the overall 6 dB resolution improvement. Two successive 1.5-bit stages of a pipelined converter with the comparator threshold offsets of  $\delta_k$  and  $\delta_{k+1}$  are assumed. If the first stage offset  $(\delta_k)$  is less than 1/8, then for each value of  $\delta_{k+1}$ ,  $\delta_k$  will not affect the second stage output density. Therefore, offsets impact of less than 1/8 is fully canceled out by the latter stages. Similarly, the impact of less than 3/16 offsets can be removed by two offset-free stages or one stage with less than 1/8 offset followed by one offset-free stage. The offsets less than 7/32 are eliminated by three offset-free stages and less than  $(2^N-1)/(2^{N+2})$  offsets are fully canceled by N offset-free stages such that achieving 6 dB of extra resolution is possible. So, in a pipelined ADC with N successive 1.5-bit stages in which (N-1) first stages offsets are less than 1/8, 3/16, ...,  $(2^{k}-1)/(2^{k+2})$ ,..., and  $(2^{N-1}-1)/(2^{N+1})$ respectively, and its Nth stage offset in threshold level of +1/4 is  $\delta_N$ , the output residue pdf is [12]

$$f_{y_{N}}(y) =$$

$$\begin{cases}

\frac{1}{2^{N}} f_{x} \left( \frac{y - (2^{N} - 1)}{2^{N}} \right) & -1 < y < -\frac{1}{2} \\

\frac{1}{2^{N}} \left( \frac{(2^{N-1} - 1)}{2^{N}} f_{x} \left( \frac{y - 2m}{2^{N}} \right) \right) & \frac{-1}{2} < y < \frac{-1}{2} + 2\delta_{N} \\

+ f_{x} \left( \frac{y - (2^{N} - 1)}{2^{N}} \right) \right) & \frac{-1}{2} + 2\delta_{N} < y < \frac{1}{2} \\

\frac{1}{2^{N}} \sum_{m = -(2^{N} - 1)}^{(2^{N} - 1)} f_{x} \left( \frac{y - m}{2^{N}} \right) & \frac{-1}{2} + 2\delta_{N} < y < \frac{1}{2} \\

\frac{1}{2^{N}} \left( \sum_{m = -(2^{N-1} - 1)}^{(2^{N} - 1 - 1)} f_{x} \left( \frac{y - 2m}{2^{N}} \right) & \frac{1}{2} < y < \frac{1}{2} + 2\delta_{N} \\

+ f_{x} \left( \frac{y + (2^{N} - 1)}{2^{N}} \right) & \frac{1}{2} + 2\delta_{N} < y < 1.

\end{cases}$$

Thus, only the offset impact of Nth stage appears in the output pdf and the previous stage offsets impact is canceled. According to (23), after many stages, the residue pdf concentrates over  $[-1/2, 1/2 + 2\delta_N]$

$$f_{y_{N}}(y) = \begin{cases} \frac{1}{2} & -\frac{1}{2} < y < -\frac{1}{2} + 2\delta_{N} \\ 1 & -\frac{1}{2} + 2\delta_{N} < y < \frac{1}{2} \\ \frac{1}{2} & \frac{1}{2} < y < \frac{1}{2} + 2\delta_{N} \\ 0 & \text{otherwise.} \end{cases}$$

(24)

Comparing (18) and (24) shows the quantization leakage and decreasing the resolution improvement compared with the ideal converter. Using (20), the converter SQNR improvement is obtained as follows:

$$\Delta SQNR_R = 10 \log_{10} \left( \frac{4}{24 \delta_N^2 + 1} \right) \text{ dB.}$$

(25)

Based on the above explanation, considering the offsets in both  $\pm 1/4$  threshold levels, we can see that in a converter with N successive 1.5-bit stages in which (N-1) first stages offsets are less than 1/8, 3/16,...,  $(2^k-1)/(2^{k+2})$ ,..., and  $(2^{N-1}-1)/(2^{N+1})$  respectively, the offsets impacts of the stages before the last stage on the output residue density is eliminated and only the last stage offset impact can be seen in the output pdf. Since offsets in each stage of the multi-stage converter will differently affect the stages residue probability density functions, simulation can better reveal different offsets impacts.

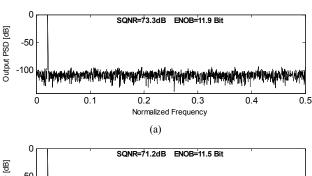

To clarify the issue, simulations were performed for three 11-bits pipelined ADCs including  $10\times1.5$ -bit stages and an ideal 1-bit backend flash. The comparator threshold offsets of 9 first 1.5-bit stages are less than  $(2^k-1)/(2^{k+2})$ , (k=1,2,...,9) and the offset of the tenth 1.5-bit stage was

**Fig. 7.** Output PSD of an 11-bits pipelined ADC in which the comparator threshold offsets of 9 first 1.5-bit stages are less than  $(2^k - 1)/(2^{k+2})$ , (k = 1,2,...,9) and the offset of the tenth 1.5-bit stage was set to: (a) 0, (b) 1/8, (c) 1/4.

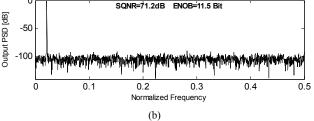

set to 0, 1/8 and 1/4, respectively. The output PSD of these ADCs for a full-scale sinusoidal input are shown in Fig. 7. It is observed that the ENOB of the converter with the offset-free tenth 1.5-bit stage is equal to the ideal converter of Fig. 6(a). Also, Figs. 7(b) and (c) show that converter noise floor rises with increasing the tenth stage offset which decrease the overall 6 dB resolution improvement. The different stages residue pdfs of the converter of Fig. 7(a) for a triangular input density is shown in Fig. 8. As it is expected, the impact of the threshold offsets of the first 1.5-bit stages in final residue pdf is eliminated.

In the calibration and correction of the error caused by the nonidealities in pipelined ADC, more importance is given to the first stages [19–21]. It was shown that in respect with the extent of the impact on the converter extra resolution, the offset errors of the final stages are more significant than those of the first stages. Therefore, more care should be taken of the offsets of the final stages in designing the converter.

### 6. Comparison with Previous Studies

A comparison of the proposed approach with previous studies is summarized in Tab. 2. In this approach in addition to the analysis of the residual densities for each arbitrary input pdf, it is possible to extract the statistical properties of the converter quantization noise such as uniformity

Fig. 8. The stages residue pdfs of an 11-bits pipelined ADC including 10×1.5-bit stages and a 1-bit backend with comparator offsets of Fig. 8 and zero offset in the tenth stage for triangular input pdf.

|                                                       | Ref [9]      | Ref [10]     | This approach |

|-------------------------------------------------------|--------------|--------------|---------------|

| Full-bit Structure                                    | ✓            | _            | ✓             |

| Half-bit Redundant Structure                          | $\checkmark$ | $\checkmark$ | $\checkmark$  |

| Arbitrary Input pdf                                   | $\checkmark$ | _            | $\checkmark$  |

| Joint pdf Analysis in Full-bit<br>Structure           | ✓            | _            | ✓             |

| Joint pdf Analysis in Half-bit<br>Redundant Structure | _            | _            | ✓             |

| Sub-ADC Comparator Offset<br>Errors                   | _            | ✓            | ✓             |

Tab. 2. The performance summary and comparison.

and independence from the input. It also makes it possible to examine the impact of sub-ADC comparator offset errors on the residues probability density function.

The proposed analysis approach can be extended to the joint pdf of output residues in the full-bit and half-bit redundant structures at different times. It can be shown that with increasing the number of converter bits, residues joint pdf converges to uniformity. This fact shows the statistical independency of the different stages residue in pipelined ADC for the very high number of bits. For this reason in [22] half-bit redundant pipelined ADC has shown a good performance in random number generation.

### 7. Conclusion

A new approach to analyze the stages residue pdfs in pipelined converter has been presented. This work was performed based on the fundamental theorem for function of a random variable to map stage input pdf to its output density. It was shown that residue pdf converges to uniformity. For the stages with half-bit redundancy, this uniformity is accompanied with an extra bit of resolution. Also, the minimum number of stages required to achieve a given value of resolution improvement were studied. Examining the allowable comparator offsets in different stages, it was observed that with decreasing the offset errors in final stages, offset errors impact of the first stages on the final residue pdf and the total converter resolution can be eliminated.

#### References

- [1] CHEN, C.-Y., WU, J., HUNG, J.-J., et al. A 12-bit 3 GS/s pipeline ADC with 0.4 mm2 and 500 mW in 40 nm digital CMOS. *IEEE Journal of Solid-State Circuits*, 2012, vol. 47, no. 4, p. 1013 –1021. DOI: 10.1109/JSSC.2012.2185192

- [2] MEDAWAR, S., HANDEL, P., BJORSELL, N., JANSSON, M. Postcorrection of pipelined analog-digital converters based on input-dependent integral nonlinearity modeling. *IEEE Transactions on Instrumentation and Measurement*, 2011, vol. 60, no. 10, p. 3342–3350. DOI: 10.1109/TIM.2011.2126870

- [3] SUNDSTROM, T., MURMANN, B., SVENSSON, C. Power dissipation bounds for high-speed Nyquist analog-to-digital converters. *IEEE Transactions on Circuits and Systems I, Regular Papers*, 2009, vol. 56, no. 3, p. 509–518. DOI: 10.1109/TCSI.2008.2002548

- [4] LE, B., RONDEAU, T.W., REED, J.H., BOSTIAN, C.W. Analog-to-digital converters. *IEEE Signal Processing Magazine*, 2005, vol. 22, no. 6, p. 69–77. DOI: 10.1109/MSP.2005.1550190

- [5] GUSTAVSSON, M., WIKNER, J. J., TAN, N. N. CMOS Data Converters for Communications. Kluwer, 2002.

- [6] WIDROW, B. A study of rough amplitude quantization by means of Nyquist sampling theory. *IRE Transactions on Circuit Theory*, 1956, vol. 3, no. 4, p. 266–276. DOI: 10.1109/TCT.1956.1086334

- [7] WIDROW, B., KOLLAR, I. Quantization Noise-roundoff Error in Digital Computation, Signal Processing, Control, and Communication. Cambridge, U. K.: Cambridge University, 2008.

- [8] SPIRAD, A. B., SNYDER, D. L. A necessary and sufficient condition for quantization errors to be uniform and white. *IEEE Transactions on Acoustics, Speech, and Signal Processing*, 1977, vol. ASSP-25, no. 5, p. 442–448. DOI: 10.1109/TASSP.1977.1162977

- [9] LEVY, B. A propagation analysis of residual distributions in pipeline ADCs. *IEEE Transactions on Circuits and Systems I, Regular Papers*, 2011, vol. 58, no. 10, p. 2366–2376. DOI: 10.1109/TCSI.2011.2142850

- [10] GUERBER, J., GANDE, M., MOON, U.-K. The analysis and application of redundant multistage ADC resolution improvements through PDF residue shaping. *IEEE Transactions on Circuits and Systems I, Regular Papers*, 2012, vol. 59, p. 1733–1742. DOI: 10.1109/TCSI.2011.2180435

- [11] PAPOULIS, A., PILLAI, S. U. Probability Random Variables and Stochastic Processes. 4th ed. 2002. ISBN-13: 978-0071226615

- [12] FATEMI-BEHBAHANI, E., FARSHIDI, E., ANSARI-ASL, K. A new approach to analysis of residue probability density function

- in pipelined ADCs. *Integration, The VLSI Journal*, 2016, vol. 52, no. 1, p. 51–61. DOI: 10.1016/j.vlsi.2015.08.003

- [13] LI, J., MOON, U. K. Background calibration techniques for multistage pipelined ADC's with digital redundancy. *IEEE Transactions on Circuits and Systems II, Analog and Digital Signal Processing*, 2003, vol. 50, no. 9, p. 531–538. DOI: 10.1109/TCSII.2003.816921

- [14] MURMANN, B., BOSER, B. E. Digital domain measurement and cancellation of residue amplifier nonlinearity in pipelined ADCs. *IEEE Transactions on Instrumentation and Measurement*, 2007, vol. 56, no. 6, p. 2504–2514. DOI: 10.1109/TIM.2007.907950

- [15] KEANE, J. P., HURST, P. J., LEWIS, S. H. Digital background calibration for memory effects in pipelined analog-to-digital converters. *IEEE Transactions on Circuits and Systems I, Regular Papers*, 2006, vol. 53, no. 3, p. 511–525. DOI: 10.1109/TCSI.2005.858760

- [16] CHO, T., GRAY, P. R. A 10 b, 20 Msamples, 35 mW pipeline AD converter. *IEEE Journal of Solid-State Circuits*, 1995, vol. 30, no. 3, p. 166–172. DOI: 10.1109/4.364429

- [17] KARANICOLAS, A., LEE, H.-S., BARCRANIA, K. A 15b 1-Msample/s digitally self-calibrated pipeline ADC. *IEEE Journal of Solid-State Circuits*, 1993, vol. 28, no. 12, p. 1207–1215. DOI: 10.1109/4.261994

- [18] LEWIS, S., FETTERMAN, H., GROSS, G., et al. A 10-b 20 Msample/s analog-to-digital converter. *IEEE Journal of Solid-State Circuits*, 1992, vol. 27, no. 3, p. 351–358. DOI: 10.1109/4.121557

- [19] YUAN, J., FUNG, S. W., CHAN, K. Y., XU, R. A 12-bit 20 MS/s 56.3 mW pipelined ADC with interpolation-based nonlinear calibration. *IEEE Transactions on Circuits and Systems I, Regular Papers*, 2012, vol. 59, no. 3, p. 555–565. DOI: 10.1109/TCSI.2011.2167272

- [20] SUN, N. Exploiting process variation and noise in comparators to calibrate interstage gain nonlinearity in pipelined ADCs. *IEEE Transactions on Circuits and Systems I, Regular Papers*, 2012, vol. 59, no. 4, p. 685–695. DOI: 10.1109/TCSI.2011.2169854

- [21] KEANE, J. P., HURST, P. J., LEWIS, S. H. Background interstage gain calibration technique for pipelined ADCs. *IEEE Transactions* on *Circuits and Systems I, Regular Papers*, 2005, vol. 52, p. 32–43. DOI: 10.1109/TCSI.2004.839534

- [22] PARESCHI, F., SETTI, G., ROVATTI, R. Implementation and testing of high-speed CMOS true random number generators based on chaotic systems. *IEEE Transactions on Circuits and Systems I*,

Regular Papers, 2010, vol. 57, no. 12, p. 3124–3137. DOI: 10.1109/TCSI.2010.2052515

### About the Authors ...

Esmaeil FATEMI-BEHBAHANI received the B.Sc. and M.Sc. degrees in Electrical Engineering from Amirkabir University of Technology, Tehran, Iran, and K.N.Toosi University of Technology, Tehran, Iran, in 1995 and 1998, respectively. He is currently pursuing the Ph.D. degree in Electrical Engineering at Shahid Chamran University, Ahvaz, Iran. His current research interests include mixed-signal circuits and systems, and adaptive digital calibration of pipelined ADCs.

**Ebrahim FARSHIDI** was born in Shoushtar, Iran, in 1973. He received the B.Sc. degree in 1995 from Amir Kabir University of Technology, Tehran, Iran, the M. Sc. degree in 1997 from Sharif University of Technology, Tehran, Iran, and the Ph.D. degree in 2008 from IUT, Esfahan, Iran, all in Electronic Engineering. From 2002 he has been with Shahid Chamran University, Ahvaz, Iran, where he is currently an Associate Professor of the Electrical Engineering Department. His areas of interest include current-mode circuits design, and data converters.

Karim ANSARI-ASL received the B.Sc. degree in Electronic Engineering from Semnan University, Semnan, Iran, in 1995, the M.Sc. degree in Biomedical Engineering from Iran University of Science and Technology (IUST), Tehran, Iran, in 1999, and the Ph.D. degree in Biomedical Signal Processing from the University of Rennes 1, Rennes, France, in 2005. From 2005 to 2007, he was post-doctoral fellow at University of Rennes 1 and University of Geneva. Since 2008, he has been an Assistant Professor with the Electrical Engineering Department, Shahid Chamran University, Ahvaz, Iran. His research interests include biomedical engineering, and digital signal and image processing.